Symulacje układów cyfrowych z wykorzystaniem bramek logicznych, dekoderów i multiplekserów¶

Cel ćwiczenia¶

Celem ćwiczenia jest poznanie podstawowych funktorów logicznych z szeregu cyfrowych układów scalonych TTL i CMOS oraz poznanie działania i zastosowania elementów średniej skali integracji multipleksera i dekodera, które to układy kombinacyjne służące do przetwarzania informacji.

Wymagane wiadomości¶

Znajomość budowy bramek logicznych w technologii TTL i CMOS, umiejętność realizacji układu na podstawie schematu, znajomość budowy dekodera i multipleksera oraz ich zasady działania.

Prawa techniki cyfrowej:

Zmienne logiczne przyjmują dwie wartości dyskretne:

- zero logiczne: „0” lub „L”

- jedynka logiczna: „1” lub „H”

Podstawowe działania, związki pomiędzy zmiennymi logicznymi:

- iloczyn (koniunkcja): \(y=x1 \land x2=x1x2\)

- suma (dysjunkcja): \(y=x1\lor x2=x1+x2\)

- negacja: \(y=\sim x=\overline{x}\)

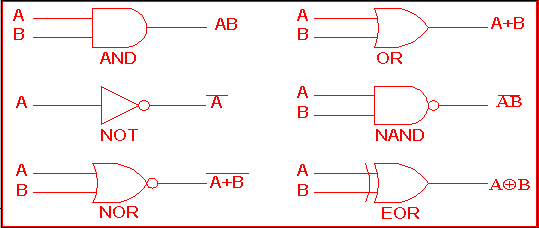

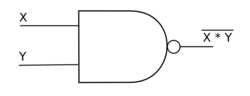

Podstawowe funktory logiczne – bramki

Bramki logiczne rys. 1 realizują proste funkcje logiczne jednej lub wielu zmiennych logicznych. Zmienną logiczną jest sygnał elektryczny występujący na wejściach i wyjściach tych układów. Poniżej przedstawione działanie logiczne podstawowych typów bramek logicznych.

|

||

|

|

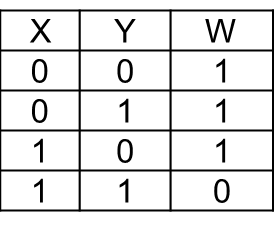

\(W=\overline{X\ast Y}\) |

|

|

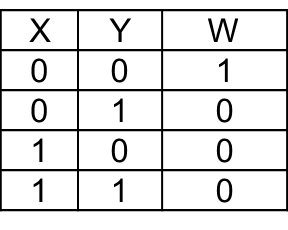

\(W=\overline{X+ Y}\) |

|

|

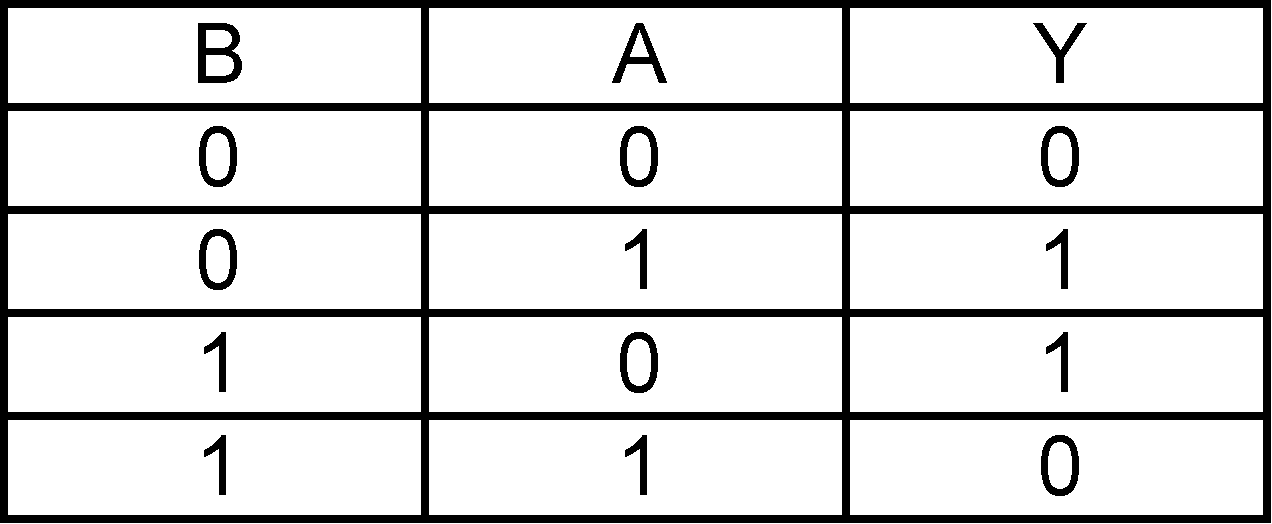

\(Y=\overline{A}B+A\overline{B}\) \(Y=(A+B)(\overline{A}+\overline{B})\) |

Rysunek 1: Symbole graficzne funktorów logicznych- bramek z tabelą działania

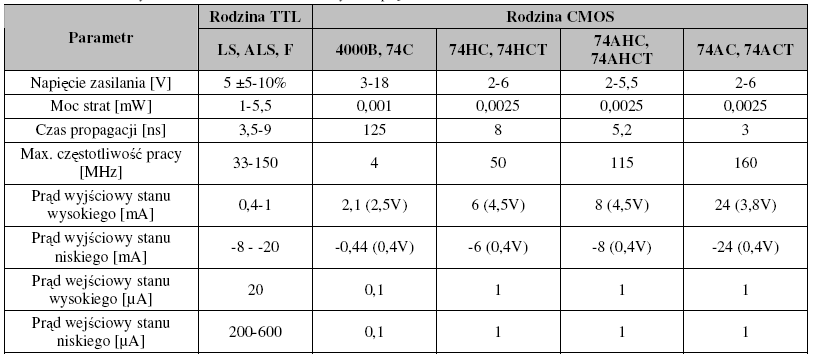

Funktory (bramki logiczne) są produkowane w postaci scalonej rys. 2 i rys. 3. Wyróżnia się dwie główne technologie wytwarzania cyfrowych układów scalonych:

TTL (ang. Transistor – Transistor Logic – logika tranzystorowo tranzystorowa) – technologia bipolarna,

Bramki TTL stand. H L S LS F Nap. zasilania \(U_{CC}[V]\) 5 5 5 5 5 4 Moc zasil. \(P_0[mW]\) 10 22 1 19 2 5 Czas propagacji \(t_p [ns]\) 10 5 33 3 5 2.8 \(P_0\,t_p[pJ]\) 100 132 33 57 10 14 Obciążalność \(N\) 10 10 10 10 20 30 \[\begin{split}U_{we}:"0"\;-0.5\div 0.8V\end{split}\]\[\begin{split}\;\;\;:"1"-2\div5.5V\end{split}\]\[\begin{split}U_{wy}:\;"0"\;0\div 0.4V\end{split}\]\[\begin{split}\;\;\;:"1"-2.4\div 5V\end{split}\]CMOS (ang. Complementary Metal – Oxide – Semiconductor) – technologia unipolarna.

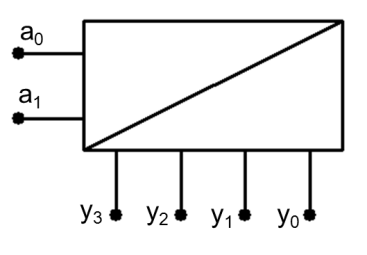

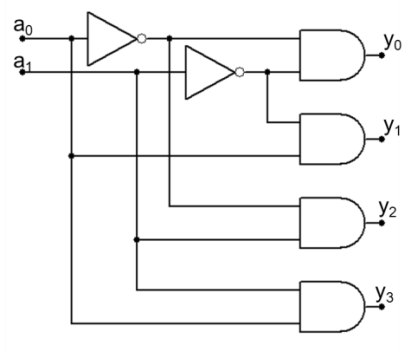

Kolejną grupę elementów kombinacyjnych stanowią układy komutacyjne zaliczamy do nich dekodery, multipleksery i demultipleksery rys. 4 i rys. 5. Dekodery są to układy kombinacyjne n / m (liczba wejść / liczba wyjść) przekształcające określony kod wejściowy o długości m na kod wyjściowy „1 z n”. Dekoder posiada m wyjść, a każdemu ze słów wyjściowych jest przyporządkowany sygnał aktywny (\(1\) lub \(0\)), pojawiający się tylko na jednym z m wyjść, pozostałe zmienne wyjściowe mają wartość przeciwną.

Dekoder 1 z n (BCD)¶

|

|

|

|

\(y_0=\overline{a_1}\overline{a_0} \quad y_1=\overline{a_1} a_0\) \(y_2=y_0=a_1\overline{a_0}\quad y_3=\overline{a_1}\overline{a_0}\) |

|

Rysunek 4: Symbol, tabela działania, schemat ideowy i opis funkcyjny dekodera.

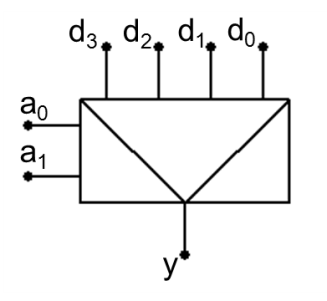

W systemach cyfrowych często istnieje potrzeba przesyłania selektywnie wybranej informacji dwójkowej. Do tego celu służy technika multipleksowa. Multiplekser przekazuje sygnał cyfrowy z jednego z wejść na pojedyncze wyjście, tzw. linię przesyłową, natomiast demultiplekser przenosi sygnał cyfrowy z pojedynczego wejścia na jedno z wielu wyjść. Nazwa obydwu elementów pochodzi od łacińskiego „multiplex” oznaczającego „wiele razy”.

Multiplekser (2 na 4)¶

Przebieg ćwiczenia¶

Badanie elementarnych funktorów NAND Sporządzić tabelę zależności dla 2 i 3 wejściowych funktorów NAND (środowisko LabVIEW lub CEDAR Logic). Wyniki z pomiaru zanotować w tabeli:

\(Y=\overline{AB}\) \(Y=\overline{ABC}\) a b c \(y_{teor.}\) \(y_{1zm.}\) \(y_{2zm.}\) 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Z dostępnych funktorów 2-wejsciowych NAND skonstruować funktor 3-wejściowy NAND. Wyniki pomiarów zamieścić w powyższej tabelce.

Badanie elementarnych funkcji boolowskich

Zrealizować (za pomocą funktorów NAND) następujące funkcje i sporządzić dla nich tablicę zależności (tabelka jak w pkt. 1). Do praktycznej realizacji funkcji wykorzystać środowisko LabVIEW lub CEDAR Logic.

\[Y=ab+bc+ac\]\[Y=\overline{a}b+a\overline{b}\]\[Y=a\overline{b}c+ab\overline{c}+abc\]Badanie podstawowych właściwości multipleksera i dekodera Dla multipleksera i dekodera sporządzić tabelkę zależności między sygnałami wyjściowymi a wejściowymi i adresowymi. Kolumnę z sygnałami wyjściowymi wypełnić na podstawie pomiarów (środowisko LabVIEW lub CEDAR Logic).

Opracowanie wyników¶

W sprawozdaniu:

- Sporządzić schematy badanych układów wraz z tabelą działania oraz dokonać transformacji na podstawie praw algebry Boole’a do funktorów NAND.

- Opisać zasadę działania dla dekodera 3x8 oraz 3x8 dla multipleksera na podstawie przebadanych multiplekserów i dekoderów.

Literatura¶

| [Filpkowski2005] | A. Filpkowski, „Ukady elektroniczne analogowe i cyfrowe” EIT 2005r. |

| [Kalisz2002] | J. Kalisz, „Podstawy elektroniki cyfrowej” WKŁ 2002r |

| [Horowitz2002] | P. Horowitz, W Hill, „Sztuka elektroniki” WKŁ 2002r. |

| [Pioro2005-5] | M. Pióro, „Podstawy elektroniki” WSiP 2005r. |

| [Chwaleba2002] | A. Chwaleba, „Pracownia elektroniczna” WSiP 2002r. |

| [Pioro1996-5] | M. Pióro „Podstawy elektroniki, część I i część II”, Warszawa 1996r. |

| [Piecha1985] | J. Piecha, „Elementy cyfrowe TTL” Skrypt Uniwersytetu Śląskiego 1985r. |

Testy do rozdziału¶

Test 1¶

Test 2¶

Test 3¶

Test 4¶

Test 5¶

Test 6¶

Test 7¶

Test 8¶

Test 9¶

Test 10¶

Pytania kontrolne¶

- Jakie napięcie reprezentuje stan wysoki w technice TTL

- Ilu tranzystorów MOS potrzeba by zbudować bramkę NAND

- Kiedy funkcja Y =AB będzie zawsze \(Y =1\)

- Jak zrealizować funkcję NOT bramkami NAND

- Czy dekoder posiada wejścia a jeśli tak to jakie

- Kiedy Y =AB będzie zawsze \(Y =0\)

- Co to jest multiplekser

- Do czego służy dekoder

- Jak zrealizować funktor EXOR z bramek NAND

- Jak zrealizować funktor NOT z bramek NAND